工学部 電子情報システム工学科

森貴之 研究室

MORI Takayuki

LABORATORY

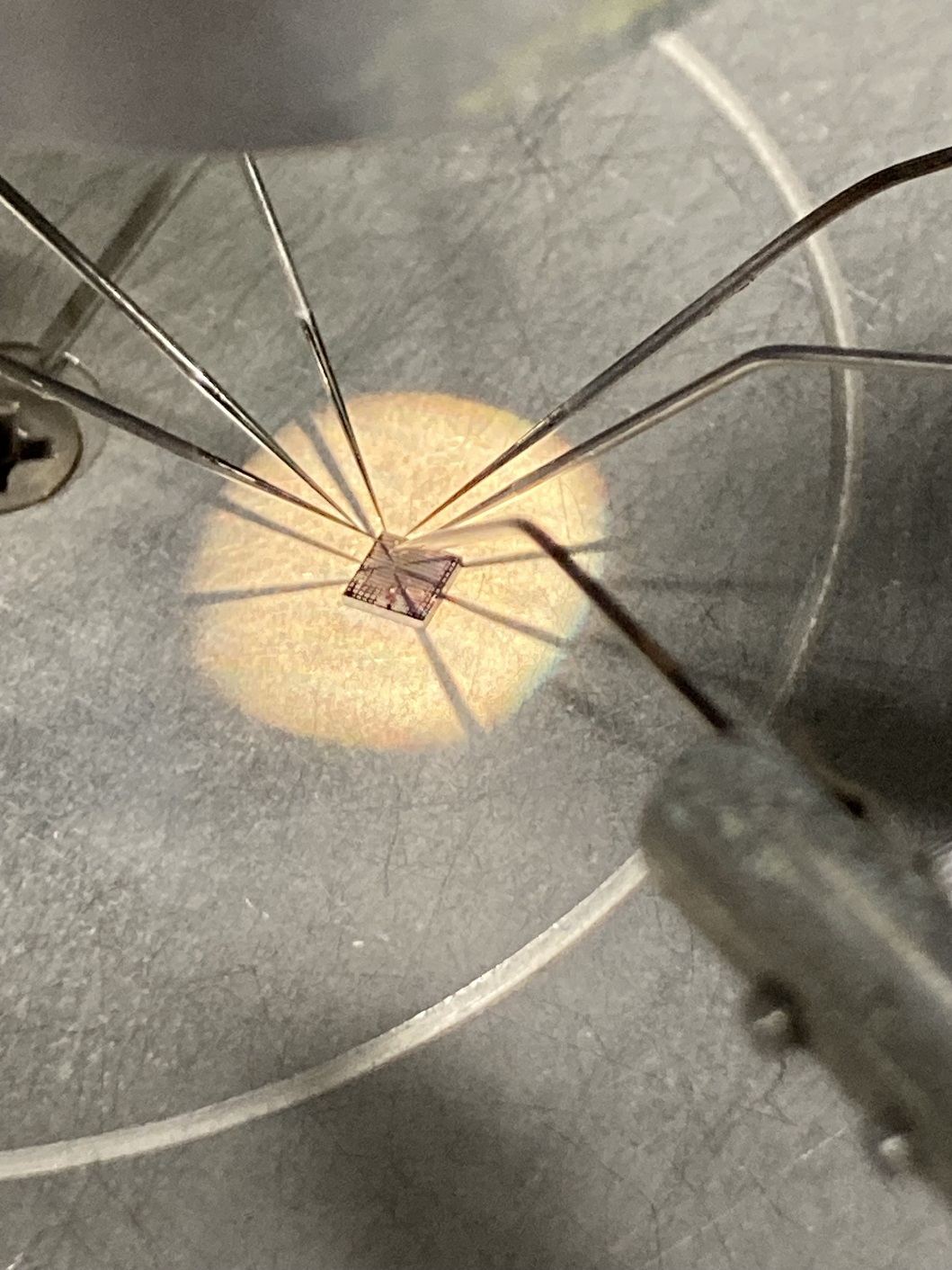

次世代型コンピューティング用極低消費電力デバイス・回路の研究

情報化社会が進み、データを処理するコンピュータにはますます高性能化・低消費電力化が求められています。その中で、次世代型コンピューティングとして人間の脳機能を電子回路で模倣するニューロモルフィックチップや量子コンピュータが注目されています。研究室では上に挙げたニューロモルフィックチップを実現するためのデバイスや、量子コンピュータを制御するためのCryo-CMOS技術の開発に取り組んでいます。

キーワード

- シリコン半導体デバイス

- 集積回路

- ニューロモルフィック

- 極低温(Cryogenic)CMOS

教員紹介

TEACHERS

森貴之 准教授・博士(工学)

略歴

専門分野

専門:ニューロモルフィック、エネルギーハーベスティング、steep subthreshold slope、SOI

学生へのメッセージ

高専生時代に量子力学という物理学の分野をかじって衝撃を受け、その応用分野である半導体デバイスに興味を持ち、大学生時代から現在まで関わっています。目視できない微小な世界で動く電子の動きを想像する楽しさを共有できればと思っています。

自分で能動的に動けば、大学では本当に様々なことを学べます。将来にわたって関わりたいと思える何かをぜひ探してみてください。

担当科目

プロジェクトデザイン入門(実験)(電気・電子) 電気回路基礎 電気回路Ⅰ 電子工学(先取り履修・オンデマンド授業) 電子工学(先取り履修・オンデマンド授業) プロジェクトデザインⅢ(森貴之研究室) 専門教養特別科目(教養としての電気電子工学) プロジェクトデザイン実践(実験)(電気・電子) 光・電子デバイス工学 光・電子デバイス統合特論

研究業績

RESEARCH RESULTS

論文

- Suppressed Thermal Conduction to Adjacent Devices and Enhanced Hotspot Confinement in 200 nm SOI MOSFETs at Cryogenic Temperatures

- Impact of Contacts and Heatsinks on Heat Accumulation in Cryogenic SOI MOSFETs

- Emulation of Neuronal Behavior using Steep Subthreshold Slope GCCI SOI-Tr with High Impedance and Low Voltage Swing

- Transient analysis of steep subthreshold slope gate-controlled carrier-injection silicon-on-insulator transistor for ultra-low power applications

- Evaluation of Transient Characteristics on Steep Subthreshold Slope “Gate-Controlled Carrier-Injection SOI-Transistor”

- Enhanced Self-Heating and Reduced Thermal Conduction to Adjacent Devices at Cryogenic Temperatures with 200 nm SOI MOSFETs

- Reducing Short-Circuit Current of CMOS Inverter Circuits with “PN-Body Tied SOI-FET”

- Steep Subthreshold Slope Gate-Controlled Carrier-Injection SOI Transistor for Ultralow Power Applications

詳しい研究業績はこちら